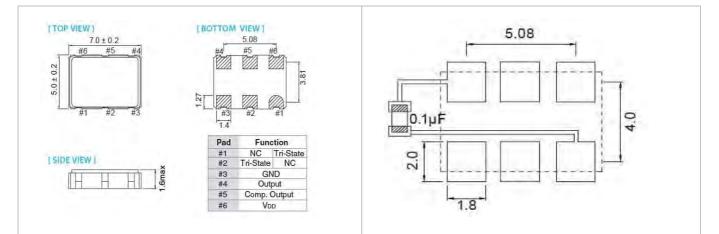

# OT Type 7.0 x 5.0 mm SMD HCSL Crystal Oscillator

## **FEATURE**

- Typical 7.0 x 5.0 x 1.5 mm hermetically sealed ceramic package.

- Very low jitter performance : Max. 0.5 pS RMS from 12k-20MHz.

- Tight symmetry (45 to 55%) available.

- Tri-state enable/disable.

- High-speed current steering logic (HCSL) output.

## **TYPICAL APPLICATION**

- PCI-Express

#### **RoHS Compliant Standard**

#### **ELECTRICAL SPECIFICATION**

| Parameter                                   | HCSL   |        |        |        |        |

|---------------------------------------------|--------|--------|--------|--------|--------|

|                                             | 3.3V   |        | 2.5V   |        | Unit   |

|                                             | Min.   | Max.   | Min.   | Max.   |        |

| Supply Voltage Variation (VDD)              | VDD-5% | VDD+5% | VDD-5% | VDD+5% | V      |

| Frequency Range                             | 90     | 125    | 90     | 125    | MHz    |

| Standard Frequency                          | 100    |        |        |        | IVITIZ |

| Supply Current                              |        |        |        |        |        |

| $90MHz \leq F0 \leq 125MHz$                 | -      | 30     | -      | 30     | mA     |

| Output Level                                |        |        |        |        |        |

| Output High (Logic "1")                     | 0.6    | -      | 0.58   | -      | V      |

| Output Low (Logic "0")                      | -      | 0.15   | -      | 0.15   |        |

| Transition Time:Rise/Fall Time+             | -      | 0.5    | -      | 0.5    | nSec   |

| Start Time                                  | -      | 3      | -      | 3      | mSec   |

| Tri-State(Input to Pin 2 or Pin 1)          |        |        |        |        |        |

| Enable                                      | 0.7VDD | -      | 0.7VDD | -      | V      |

| Disable                                     | -      | 0.3VDD | -      | 0.3VDD |        |

| RMS Phase Jitter (integrated 12KHz ~ 20MHz) |        |        |        |        |        |

| $90MHz \leq F0 \leq 125MHz$                 | -      | 0.5    | -      | 0.5    | pSec   |

| Aging                                       | -      | ±3     | -      | ±3     | ppm    |

| Storage Temp. Range                         | -55    | 125    | -55    | 125    | °C     |

Standard frequencies are frequencies which the crystal has been designed and does not imply a stock position

+Transition times are measured between 20% and 80% of VDD

#### FREQ. STABILITY vs. TEMP. RANGE

冠杰电子

| ppm<br>Temp. (°C) | ±25 | ±50 |

|-------------------|-----|-----|

| -10~+60           | 0   | 0   |

| -20~+70           | 0   | 0   |

| -40~+85           | Δ   | 0   |

\* O: Available △:Conditional X: Not available \*Inclusive of calibration @ 25℃, operating temperature range, input voltage variation,